Cadence has fine-tuned its AI-driven RTL-to-GDS digital flow, as well as its AI-driven verification flow, for the Arm Neoverse V2 CPU. The company also created corresponding 5-nm and 3-nm Rapid Adoption Kits (RAKs). These tools not only help designers achieve power, performance, and area (PPA) targets faster, but also enable optimal verification throughput and preparedness for Arm SystemReady compliance.

![]()

The digital RAKs leverage AI capabilities to automate and scale digital chip design, delivering better PPA and increasing designer productivity. They employ a smart hierarchy flow that improves turnaround times for large, high-performance CPUs, while an activity-aware power optimization engine reduces dynamic power consumption.

The verification flow provides Neoverse V2 designers with pre-silicon server base system architecture (SBSA) compliance verification and efficient PCI Express integration. Helium gearshift technology enables customers to position workloads in a hybrid environment before shifting to a fully accurate RTL environment, offering detailed verification using either the Palladium or Protium platforms.

To learn more about how to verify Arm-based designs using digital and verification solutions from Cadence, click here.

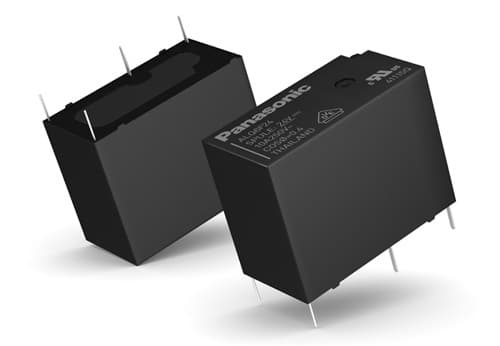

Find more datasheets on products like this one at Datasheets.com, searchable by category, part #, description, manufacturer, and more.