The companies behind Google’s OpenTitan project recently announced the commercial availability of what they called the world’s first chip with open-source hardware security baked directly into it.

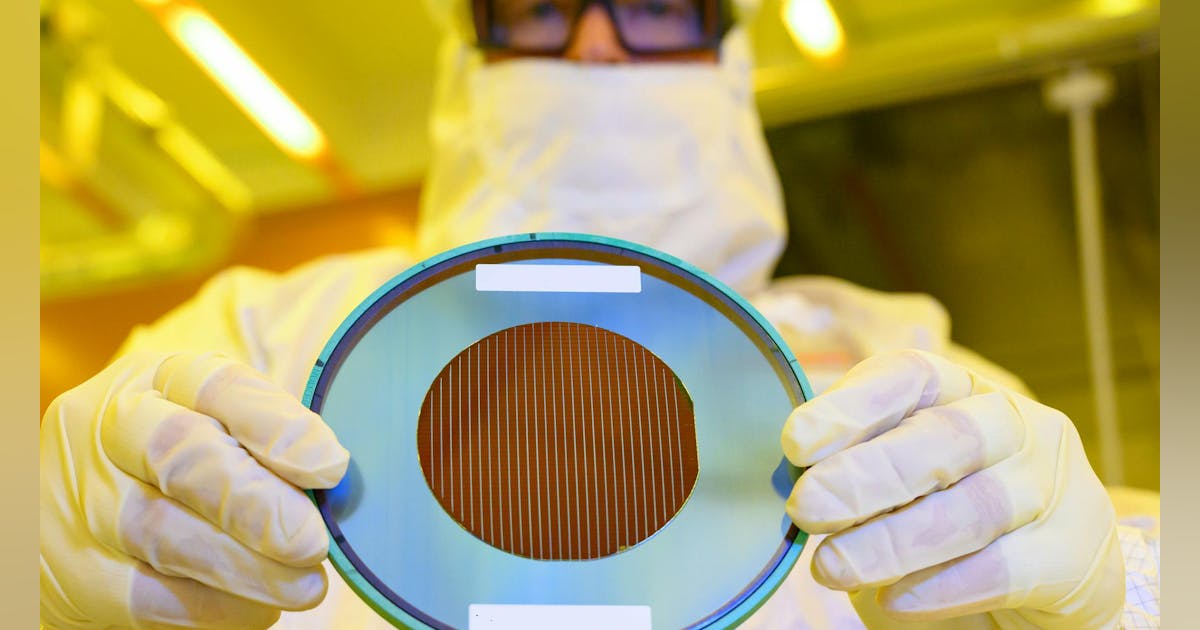

While OpenTitan will be the first commercial-grade chip on the market modeled on Linux and other open-source software, Dominic Rizzo, one of the founders of OpenTitan, said he’s confident it will not be the last. Under development for half a decade and based on OpenTitan’s discrete “Earl Grey” chip design taped out in mid-2023, the chip is designed to be a universally accessible hardware root of trust (RoT).

The milestone shows that the concept of open source is not inherently incompatible with silicon, said Rizzo, now CEO of zeroRISC, a startup building a secure embedded operating system (OS) that can take advantage of the OpenTitan hardware RoT and the firmware that will run on top of it. “It’s not proprietary, and it’s not a test chip, but it’s going to be a very high-volume security chip,” he told Electronic Design.

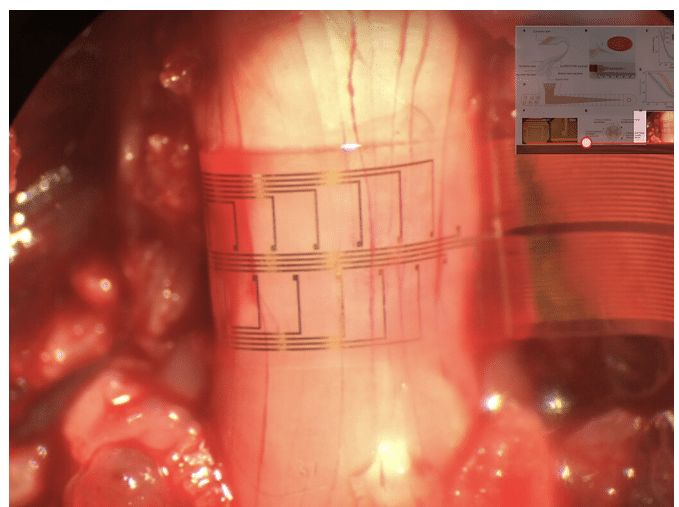

In its capacity as the hardware RoT, the chip is designed to make sure that the hardware in a system, and software running on it, remains in their intended, trustworthy state. It ensures components in a system boot securely using only authorized, verifiable code. And it’s hardened against fault injection and other physical attacks on the hardware, which is relevant to many of the tiny devices comprising the Internet of Things (IoT).

The concept of open silicon has been gaining ground in the semiconductor industry lately, largely due to the rapid growth of the open RISC-V instruction set architecture (ISA). The RISC-V ISA acts as the interface that the software uses to communicate with the processor’s hardware. Companies can adopt it to develop CPU cores or other IP without being limited by the same constraints as Arm or other architectures. The “Ibix” CPU at the heart of the OpenTitan chip is itself based on RISC-V.

Even though the underlying architecture is open to all, most companies are building CPU cores and other IP based on RISC-V themselves behind closed doors, using it as any other tool in the toolbox.

But according to Russo, the companies and other partners behind the OpenTitan project are taking the concept of open hardware a step further by building the chip itself and the IP inside as a collective.

“Silicon Commons”: Designing Chips Out in the Open

Google launched OpenTitan in 2019, building on the development of its own in-house hardware RoT, called Titan. Besides the formal partners in the project, including a wide range of semiconductor firms and academic partners, the OpenTitan chip was developed by a large and growing community of independent coders and other contributors worldwide. The project is supported and maintained by lowRISC, a neutral, independent non-profit.

While it was based on the same principles behind Linux and other efforts in open-source software, OpenTitan presented unique difficulties. Designing a modern chip is a large, enormously complex engineering problem that can take several years and as many as thousands of engineers to tackle. Rizzo said the high cost of hardware development relative to software also raises the difficulty level.

The inability to update or upgrade the underlying hardware after it’s manufactured adds to the complexity. “There are huge risks with silicon,” said Rizzo. “You sort of get one shot with it, and it works, or it doesn’t.”

The other problem is related to personnel. Many of the engineers with experience in the world of open-source software aren’t as familiar with the traditional “waterfall” model of hardware design. In contrast, many hardware engineers that are in the best position to contribute to OpenTitan and other open chip designs aren’t as clued into the ins and outs of open-source product development.