![]()

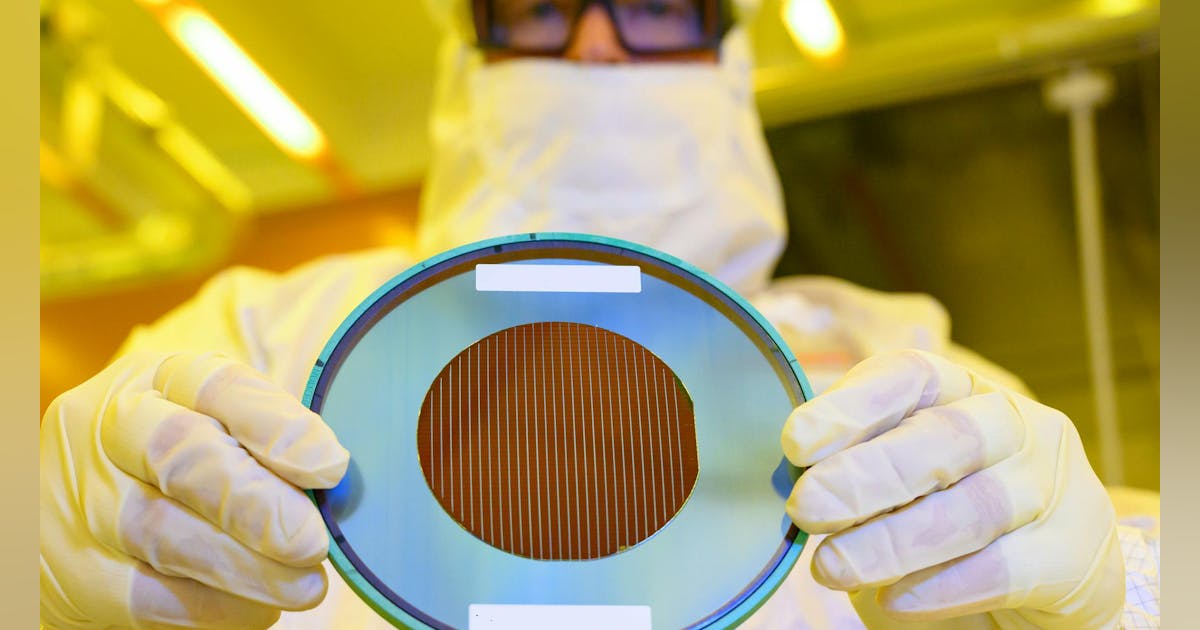

One of the largest vendors of embedded processors has independently developed a CPU core for the 32-bit general-purpose RISC-V market; it can be used as the main CPU or on-chip subsystem and can even be embedded in an application-specific standard product (ASSP).

Renesas Electronics, which has designed and tested a 32-bit CPU core based on the open-standard RISC-V instruction set architecture (ISA), is currently sampling devices based on this new core to select customers. It plans to launch its first RISC-V-based MCU and associated development tools in the first quarter of 2024.

It’s important to note that while several MCU suppliers have announced the development of RISC-V products, Renesas is the first company to unveil a 32-bit RISC-V MCU architecture development. Also worth noting is that the Japanese chipmaker’s 32-bit MCU portfolio includes its proprietary RX Family as well as RA Family based on the Arm Cortex-M architecture.

Another important fact in Renesas’s RISC-V foray is that it has already introduced 32-bit ASSP devices for voice control and motor control built on CPU cores developed by Andes Technology. Renesas has also unveiled 64-bit general-purpose microprocessors (MPUs) built on Andes CPU cores.

![]()

The high-level block diagram highlights the 32-bit RISC-V MCU architecture development. Source: Renesas

Renesas claims its RISC-V CPU achieves a 3.27 CoreMark/MHz performance, outperforming similar architectures in performance and code size reduction. It’s a versatile CPU that is suitable for different application contexts. For instance, it can serve as a main application controller, a complementary and secondary core in system-on-chips (SoCs), and in on-chip subsystems and deeply embedded ASSPs.

Giancarlo Parodi, principal product marketing engineer at Renesas, also claims in his blog that CPU’s implementation is very efficient regarding silicon area. Besides smaller cost impact, it helps reduce operating current and leakage current during standby time. Finally, despite targeting small embedded systems, this RISC-V core provides a high level of computational throughput.

Next, in line with RISC-V ISA foreseeing several ‘extensions’ that target specific functionality more efficiently, Renesas has included extensions to improve performance and reduce code size. Additionally, the CPU core has added a stack monitor register to enhance the robustness of the application software. It will help designers detect and prevent stack memory overflows, a common issue spotted through test coverage alone.

Parodi’s blog provides more details about the CPU features and capabilities and how they assist developers in benchmarking an application and verifying its behavior. More details about its performance score will be available on the EEMBC website once the first product is unveiled in early 2024.

The RISC-V processors, known for their flexibility, are gradually making inroads in the embedded systems landscape. In this design journey, the availability of a homegrown CPU from a major MCU supplier lends RISC-V fray significant credibility in offering embedded processing solutions for a broad range of applications.

Related Content

- A Big Week for RISC-V

- Examining the Top Five Fallacies About RISC-V

- Startups Help RISC-V Reshape Computer Architecture

- Accelerating RISC-V development with network-on-chip IP

- RISC-V venture in Germany to accelerate design ecosystem

googletag.cmd.push(function() { googletag.display(‘div-gpt-ad-native’); });

–>

The post RISC-V’s embedded foray with a 32-bit MCU development appeared first on EDN.